Currently If you upload a GERBER file that has a copper fill that goes right to the edge there is no warning in the Board inspector.

I think it would be beneficial to check for this as copper filled up to the sides can lead to various functional problems, most notably short circuits between power/ground planes.

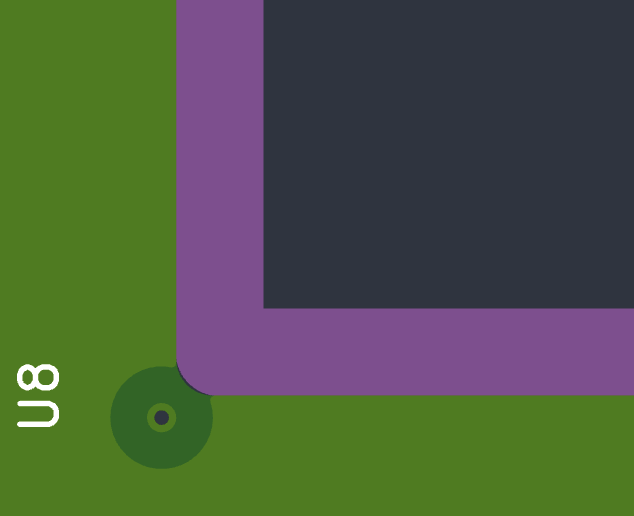

Here an example of such a situation in the board viewer:

1 Like

Just uploaded a design and Thea noticed the tolerance between copper planes/traces is to small(thanks for that service!).

The board viewer does not catch that error.

So simple request check for copper to copper spacing.

Aisler supporting KiCad board files are very nice for the consumer. It can however give problems when saving without refilling. When refilling doesn’t happen it will result in a edge to copper clearance of 0.

Same problem, someone else: Re-fill zones on Save (#14747) · Issues · KiCad / KiCad Source Code / kicad · GitLab

Proposal:

Check or visualise edge clearance on upload.

Possible solution:

KiCad has a command line interface that can be used to export layers to SVG. Exporting all copper layers, thickening the edge line to 2x 0.3mm and masking that on top of copper layers will expose the offending parts per layer.

Step 1:

kicad-cli.exe pcb export svg -l Edge.Cuts,F.Cu --exclude-drawing-sheet '.\my-project.kicad_pcb'

Step 2:

Find and replace the edge line thickness, change to 0.6mm (SVG is just XML)

Step 3:

Use an SVG tool (Like Inkscape) to mask Copper layers with the thickened edge. You could use a client-side library like SVG.js v3.0 | Other Elements.

Step 4:

Compare resulting layer with a blank canvas: blank canvas means no edge violations. If errors are found the SVG can be shown to the uploader.