Hi all,

this is my first post here, nice web site / tooling btw! hope it’ll eat my screenshots (down below) which I need to even ask my question on which I am looking for help;)

I’ve got a problem with defining correct PCB outlines with cutouts using KiCad 7.

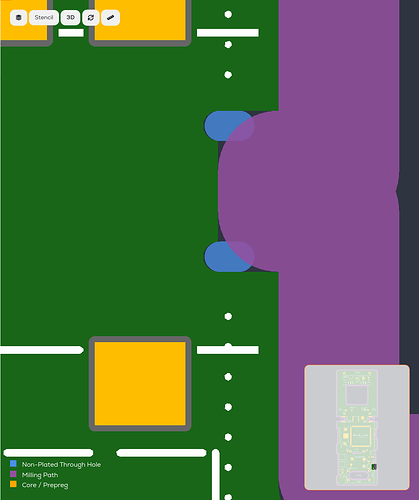

I’ve checked my PCB in an early stage using the Aisler online tools, and one issue I identified is that the outline manufacturing apparently uses both mill and drill (which is good/correct I guess?) - but still leaves small pieces of the PCB that should be gone:

The part is an audio jack, CUI Devices, SJ2-35954D-SMT-TR

The footprint of the part is the “official” one.

The Aisler PCB online check hasn’t anything to complain about (in this part), but I’m afraid the part wouldn’t fit.

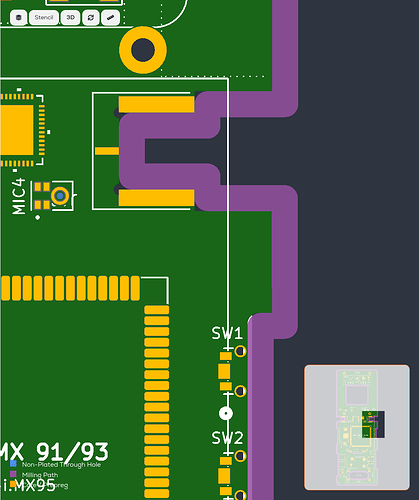

Two more problems also related to cutouts can be seen in this screenshot from the Aisler online PCB check:

The top part contains a SMA jack:

Rosenberger, 32K242-40ML5

for which I could not find a footprint, so I’ve created one based on the datasheet, but obviously it has issues (the cutout) which would also prevent the part to fit.

Finally, the bottom part shows a tiny gap in the corner next to “SW1”, the mill diameter seems slightly larger than what I used when drawing the outline in KiCad. This wouldn’t be a blocker issue … I am just wondering why?

I am sorry if those are newbie questions, I am actually a SW developer only getting into PCBs and such, so please excuse, but any tip would be absolutely appreciated.

My own footprint has bugs … I can do more experiments/design to try figuring it out … but my first issue with the CUI audio jack, I am pretty lost on this, because it is the official footprint which I use, and the 3D rendering (including Step models of the part) look perfect - but not the Aisler 3D view.

Thanks a lot,

Cheers,

/Tobias