4 Layer 0.8mm Design Rules

Last Updated: 07/07/2025

Imperial measures are rounded from metric measurements.

Design Rule Files

Do you want to start right away? We provide design rule files for Eagle, KiCad and DipTrace on Github .

The rules listed here shall always be used as reference.

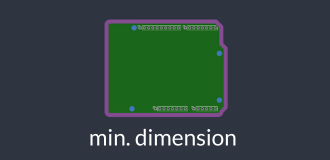

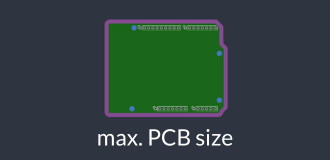

PCB Dimension

We accept PCBs within these dimensions for our prototype service, contact our support if your design does not meet these criteria.

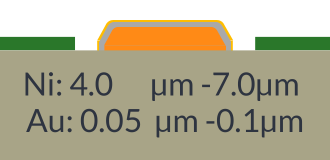

Surface Finish

We use Electroless Nickel Immersion Gold (ENIG) this surface finish offers good surface planarity and high oxidation resistance.

.

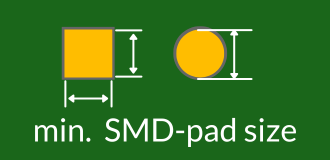

Minimum Copper Features

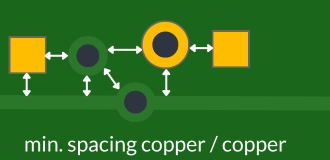

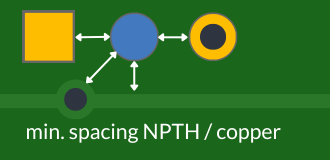

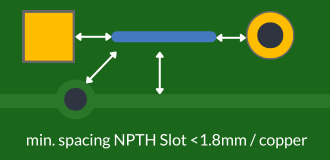

Minimum Copper Spacing / Clearance

| min. spacing copper / copper | 125 µm / 5 mil | |||

| min. spacing NPTH / copper | 250 μm / 10 mil | |||

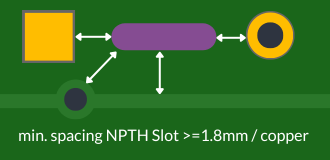

| min. spacing NPTH slot <1.8 mm / copper | 300 μm / 12 mil | |||

| min. spacing NPTH slot >= 1.8 mm / copper | 300 μm / 12 mil | |||

| min. copper to edge clearance | 300 μm / 12 mil |

Plated Through Hole (PTH)

All drills with a diameter larger than 0.45 mm are categorized as plated through hole for component mounting, we will enlarge the drill diameter to compensate for the copper plating thickness to ensure that components can be mounted more easily.

| min. PTH drill size | 0.5 mm / 0.02 in | |||

| max. PTH drill size | 5.6 mm / 0.22 in | |||

| min. PTH annular ring | 300 μm / 12 mil |

Vias

All drills with a diameter up to 0.45 mm are categorized as via drill and will not be subjected to any adjustments by us.

| min. via drill | 0.25 mm / 10 mil | |||

| max. via drill | 0.45 mm / 18 mil | |||

| min. via annular ring | 100 μm / 4 mil |

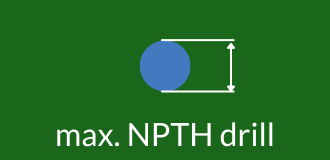

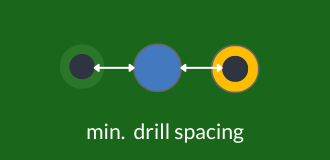

Non Plated Through Hole (NPTH)

Minimum Drill Spacing

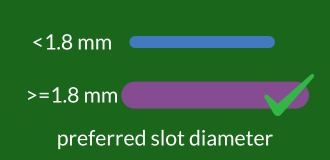

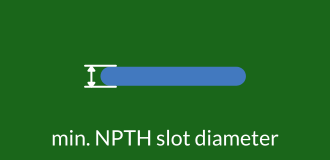

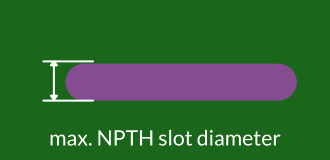

NPTH Slots

NPTHs Slots that are smaller than 1.8 mm are nibbled. This is a time-intensive process, so we reserve the right to limit the use of nibble slots in a design. Diameters above 1.8 mm will be milled and are thus preferred.

| preferred NPTH slot diameter | >= 1.8 mm / 0.07 in | |||

| min. NPTH slot diameter | 0.8 mm / 0.032 in | |||

| max. NPTH slot diameter |

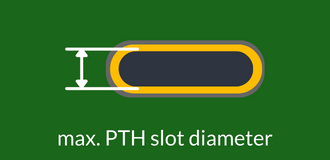

PTH Slots

| min. PTH slot diameter | 0.7 mm / 0.028 in | |||

| max. PTH slot diameter | 2.6 mm / 0.11 in | |||

| min. PTH slot annular ring | 200 µm / 12 mil |

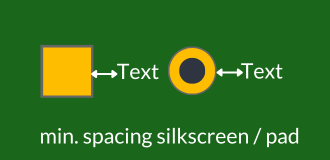

Silkscreen

We use Peters SD2692 ink for the silkscreen on our PCBs and apply it using the direct printing method. The smallest supported width is 150 µm / 6 mil, all silkscreen features with a width less of that will be adjusted. Silkscreen printed on pads is not supported, we use openings in the soldermask as reference to cut away / remove the silkscreen in the affected area. Do not use the silkscreen to produce large fillings, designs which cover more than 25% per PCB side will be rejected.

| min. silkscreen text height | 800µm / 32 mil | |||

| min. spacing silkscreen / pad | 125 µm / 5 mil | |||

| silkscreen on pad | not supported | |||

| max. Silkscreen | 25% of Board size |

Soldermask

We use high-quality Peters Elpemer AS 2467 SM-DG green soldermask which is well suited for the ENIG finish. Please refer to our soldermask specification for the electrical properties of the soldermask.

| soldermask dam between pads | recommended but not required | |||

| min. soldermask dam | 100µm / 4 mil | |||

| suggested soldermask expansion | 50 µm / 2 mil |

Castellated Edges

We manufacture castellated edges free of charge, please refer to our documentation on how you can set them up.

| castellated edges | Supported |

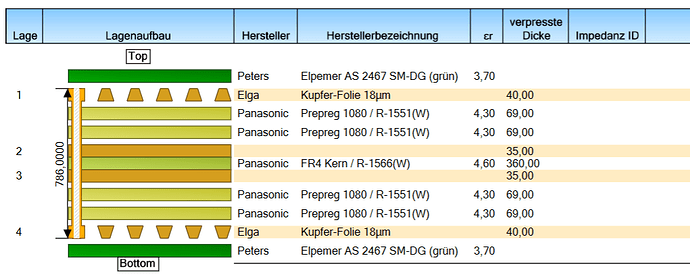

Stackup

We use Panasonic Prepreg 1080 Type R-1551(W) (58.9 KB), Peters coatings and Elga Copper foil.

Our Boards are RoHS and REACH compliant.

The following track layouts can be used to realize defined impedance. Please note that these values only provide a basic orientation. Interference factors such as angles, meanders or vias in the routing of the tracks may negatively affect the intended impedance.

Defined Impedance

These values have been taken from the 1.6mm 4 Layer Pool are have not been verified yet.

| Type | Impedance | Signal- / Reference Layer | width | space | width |

|---|---|---|---|---|---|

| Single Ended | 50 Ω | TOP / IN1, BOT / IN2 | 245 µm | - | - |

| Differential pairs | 90 Ω | TOP / IN1, BOT / IN2 | 230 µm | 165 µm | 230 µm |

| Differential pairs | 100 Ω | TOP / IN1, BOT / IN2 | 190 µm | 180 µm | 190 µm |

Additional Notes

- Buried, blind, micro or tented vias are not supported